# **STV0020**

# SATELLITE SOUND AND VIDEO PROCESSOR

ADVANCE DATA

- TWO INDEPENDENTLY PROGAMMABLE SOUND DEMODULATORS

- PLL DEMODULATION WITH 5-9MHz FRE-QUENCY SYNTHESIS

- 50/75µs, J17 OR NO DE-EMPHASIS PRO-GRAMMABLE OPTIONS

- DYNAMIC NOISE REDUCTION SYSTEM

- AUXILIARY AUDIO INPUTS

- GAIN CONTROLLED AND MUTEABLE AUDIO OUTPUTS

- COMPOSITE VIDEO 3-BIT GAIN CONTROL

- COMPOSITE VIDEO DEEMPHASIS AMPLIFIER

- 8 x 5 VIDEO MATRIX AND SWITCHES WITH GRAPHICS INPUT

- TIMER & ALARM

- 5 DIGITAL I/O's

- 8-BIT DAC OUTPUT

- FULLY CONTROLLED VIA I<sup>2</sup>C BUS

PQFP64 (Plastic Package)

ORDER CODE: STV0020

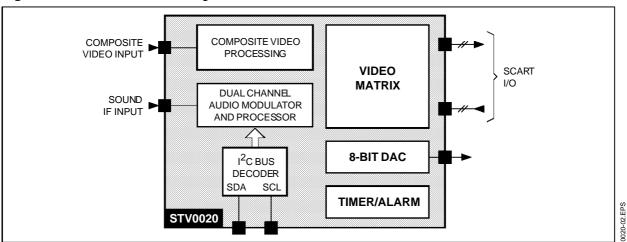

# **DESCRIPTION**

The STV0020 is a BICMOS integrated circuit for use in satellite receivers. The great variety of FM deviations, energy dispersal and subcarrier standards makes the design of satellite receivers able to receive all programs a complex task. The device has been designed to specially adapt to all known conditions in analog video and radio transmissions.

The choice of the surface mounting PQFP64 package ensures optimisation of real-estate requirements.

February 1994 1/25

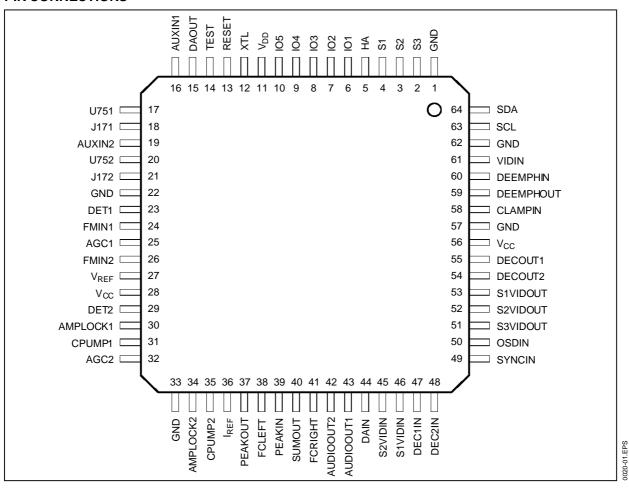

# **PIN CONNECTIONS**

# **PIN ASSIGNMENT**

| Pin | Name     | Function                           |      |

|-----|----------|------------------------------------|------|

| 1   | GND      | Digital power ground               |      |

| 2   | S3       | SCART-3 driver                     |      |

| 3   | S2       | SCART-2 driver                     |      |

| 4   | S1       | SCART-1 driver                     |      |

| 5   | HA       | Hardware address                   |      |

| 6   | IO1      | Digital input/output 1             |      |

| 7   | IO2      | Digital input/output 2             |      |

| 8   | IO3      | Digital input/output 3             |      |

| 9   | IO4      | Digital input/output 4             |      |

| 10  | IO5      | Digital input/output 5             |      |

| 11  | $V_{DD}$ | Digital 5V power supply            |      |

| 12  | XTL      | 4/8MHz quartz crystal              |      |

| 13  | RESET    | System reset                       |      |

| 14  | TEST     | Test pin                           |      |

| 15  | DAOUT    | DAC amplifier output               | ٦.   |

| 16  | AUXIN1   | Auxilliary audio input left        |      |

| 17  | U751     | 75μs de-emphasis timeconstant left | -000 |

0020-01.TBL

# PIN ASSIGNMENT (continued)

| Pin | Name            | Function                                          |  |

|-----|-----------------|---------------------------------------------------|--|

| 18  | J171            | J17 de-emphasis timeconstant left                 |  |

| 19  | AUXIN2          | Auxilliary audio input right                      |  |

| 20  | U752            | 75μs de-emphasis timeconstant right               |  |

| 21  | J172            | J17 de-emphasis timeconstant right                |  |

| 22  | GND             | RF and audio ground                               |  |

| 23  | DET1            | FM PLL filter left                                |  |

| 24  | FMIN1           | FM demodulator +ve input                          |  |

| 25  | AGC1            | AGC peak detect capacitor left                    |  |

| 26  | FMIN2           | FM demodulator -ve input                          |  |

| 27  | VREF            | 2.44V reference                                   |  |

| 28  | Vcc             | Audio 12V supply                                  |  |

| 29  | DET2            | FM PLL filter right                               |  |

| 30  | AMPLOCK1        | Amplitude detector capacitor left                 |  |

| 31  | CPUMP1          | FM PLL charge pump capacitor left                 |  |

| 32  | AGC2            | AGC peak detector capacitor right                 |  |

| 33  | GND             | Ground for volume control ANRS, VCO               |  |

| 34  | AMPLOCK2        | Amplitude detector capacitor right                |  |

| 35  | CPUMP2          | FM PLL charge pump capacitor right                |  |

| 36  | IREF            | Current reference resistor                        |  |

| 37  | PEAKOUT         | ANRS peak detector capacitor                      |  |

| 38  | FCLEFT          | Audio roll-off left                               |  |

| 39  | PEAKIN          | ANRS peak detector input                          |  |

| 40  | SUMOUT          | ANRS summing output                               |  |

| 41  | FCRIGHT         | Audio roll-off right                              |  |

| 42  | AUDIOOUT2       | Level controlled audio out right                  |  |

| 43  | AUDIOOUT1       | Level controlled audio out left                   |  |

| 44  | DAIN            | Digital/Analog Converter sense input              |  |

| 45  | S2VIDIN         | External video input 2                            |  |

| 46  | S1VIDIN         | External video input 1                            |  |

| 47  | DEC1IN          | Decoder 1 input (e.g. D2MAC)                      |  |

| 48  | DEC2IN          | Decoder 2 input (e.g. Videocrypt)                 |  |

| 49  | SYNCIN          | Digital or Analog Sync Signal Input               |  |

| 50  | OSDIN           | On-Screen-Display video input                     |  |

| 51  | S3VIDOUT        | SCART-3 video output (with OSD)                   |  |

| 52  | S2VIDOUT        | SCART-2 video output (with OSD)                   |  |

| 53  | S1VIDOUT        | SCART-1 video output (without OSD)                |  |

| 54  | DECOUT2         | Satellite decoder drive 2                         |  |

| 55  | DECOUT1         | Satellite decoder drive 1                         |  |

| 56  | V <sub>CC</sub> | Video 12V supply                                  |  |

| 57  | GND             | Video ground                                      |  |

| 58  | CLAMPIN         | Sync-tip clamp input                              |  |

| 59  | DEEMPHOUT       | Video de-emphasis output                          |  |

| 60  | DEEMPHIN        | Video de-emphasis output  Video de-emphasis input |  |

| 61  | VIDIN           | Video input buffer                                |  |

| 62  | GND             | Video input ground                                |  |

| 63  | SCL             | I <sup>2</sup> C bus clock                        |  |

| 64  | SDA             | I <sup>2</sup> C bus data                         |  |

#### PIN FUNCTION DESCRIPTION

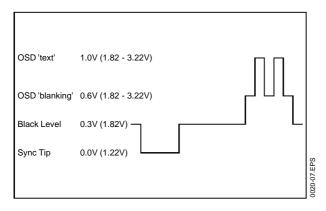

#### I - SCART DRIVERS WITH OSD

'Text' must be able to be added to the video on command with or without 'blanking'. Blanking adds either a black line around the characters or a black box for the characters to sit in. During 'blanking' the chip will output OSD 'background' level.

There are 2 basic presentation modes of OSD 'text'

- 1) OSD 'text' written on a blank screen of selectable brightness.

- 2) OSD 'text' written on top of the TV picture.

Additionally the OSD 'text' can be displayed with or without 'blanking'. The blanking from the microcontroller typically comes in two styles. Either as a line around characters or a box for the characters to sit in).

1 of 4 output levels from the SCART are required when using OSD. The diagram below shows part of a TV line displaying a small OSD. It starts with:

- a) a line sync pulse of 5μs at 0V then,

- b) 13μs at black level, followed by

- c) 2µs at OSD 'background' level.

- d) This is the OSD 'text' which has been shown as 2μs pulses going to peak white. These would be typically programmed to say 0.8V with the OSD 'background' at 0.3V (1.82V at matrix output).

In order to achieve this two DACs are used to generate the programmable voltage levels for OSD 'background' and 'text'.

The video outputs and terms are:

i) Normal video

sync tips = +1.22Vblack level = +1.82Vpeak white = +3.22V ii) Video with OSD

Video with OSD

sync tips = +1.22V

black level = +1.82V

'background' level = +1.82V to 3.22V, programmable in 8 steps of 0.2V per step 'text' = +3.22V to 1.82V, programmable in 8 steps of 0.2V per step

- iii) 'background' occurs during active video so whenever the micro generates 'blanking' it will force the SCART output to 'background' level (+1.82V to +3.22V).

- iv) 'text' occurs during active video so whenever OSD occurs the SCART output is forced to 'peak white' (+3.22V to +1.82V). In fact the OSD 'text' has higher priority than 'background' so gets applied to the signal stream after 'background'.

Described above is an ideal situation with 2.0V<sub>PP</sub> video with the bottom of the sync pulses at 1.22V. However the actual voltage of the sync tips will vary because the video is AC coupled and the picture content will change. Thus, in order to apply the 'blanking' or 'OSD' we need DC restored video the voltage of the sync tips are known and this is achieved by having 'DC level clamps' on all video input pins.

We will get correct levels on the OSD because we know the sync tip voltage (because we clamped them), so then we can select either 'background' level or 'text' level to form the OSD. The voltages given are those at Pins 51 and 52. The scart signals will be half this size.

#### Pin 2 S3

This is the tri-stateable bi-directional SCART Pin 8 driver for SCART-3. Since SCART-1,2 & 3 can be either controller or receiver SCART Pin 8 is either an output or input. Since some equipment does not follow the SCART spec fully, the micro has full control of these pins via bits in the 'control' block.

As input;  $Z_{IN}>10k\Omega <5V = logic 0, >9V = logic 1$ As output; logic 0 outputs sink 1-3mA to gnd

logic 1 outputs source 1-3mA from

Vcc-1V

Pin 3 S2

SCART-2 driver, same spec as pin 2.

Pin 4 S1

SCART-1 driver, same spec as pin 2.

#### **II - CONTROL BLOCK**

This has an I<sup>2</sup>C bus 2 wire interface. It contains registers

for the control data for the modules on the chip. It also contains 5 bi-directional tri-stateable logic I/O drives.

### Pin 1 Ground

The main power ground connection for the control logic, registers, the I<sup>2</sup>C bus interface, synthesiser & watchdog.

### Pin 5 HA

For the  $I^2C$  bus interface it is necessary to have a programmable bit on the address in case the chip address clashes with that of another chip in the application. CMOS input levels must be held high or low externally; 0 = 06h, 1 = 46h.

# Pin 6 IO1

Typically this and Pin 7 and or Pin 8 will drive external CMOS MUX switches to matrix the audio on SCARTS 2 and 3.

#### Pin 7 102

See Pin 6.

#### Pin 8 IO3

See Pin 6.

#### Pin 9 104

A general purpose I/O pin with dual functionality. It is intended to monitor a MAC decoder module signal line to see if it is receiving a MAC encoded signal.

# Pin 10 IO5

A general purpose I/O pin intended to monitor a Videocrypt decoder module signal line to see if it is receiving a Videocrypt encoded signal.

# Pin 11 V<sub>DD</sub>

Digital +5V power supply.

#### Pin 63 SCL

This is the I<sup>2</sup>C bus clock line. Clock = DC to 100kHz. Requires external pull up eg.  $10k\Omega$  to 5V.

#### Pin 64 SDA

This is the  $I^2C$  bus data line. Requires external pull up eg.  $10k\Omega$  to 5V.

#### **III - MISCELLANEOUS BITS**

#### Pin 12 XTL

This pin allows for the on-chip oscillator to be either used with a crystal to ground of 4MHz, or to be driven by an external source via a  $22k\Omega$  series resistor. The external source can be either 4MHz or 8MHz. A programmable bit in the control block removes  $a\div~2$  block when the 4MHz option is selected.

#### Pin 13 RESET

Power on reset output. This is a voltage sensitive circuit and will give a LOW output until both supplies to this chip rise to greater than 80% of their correct value. It has some hysteresis so will remain HIGH until either of the supplies falls below 65%. The output is a current sink, 4mA, with an internal  $10k\Omega$  pull-up resistor. It is possible to force the chip into or out of reset and by pass the on-chip delay.

Typical thresholds are:  $V_{DD}=5V$   $V_{CC}=12V$  power up 3.8V 9.25V power down 3.2V 7.5V

#### Pin 14 TEST

Test pin to enable scan path testing of logic. Normal operation = L Test mode = H

#### Pin 15 DAOUT

This is the LNB PSU drive which is the output of an amplifier that compares the input on Pin 44 with an 8-bit DAC. The DAC is programmed through the I2C bus interface to set the reference voltage for the LNB drive amplifier. The voltage range is 0 to 2.44 volts (2 bandgaps), hence the feedback signal must be divided down to be in this range.

# Pin 44 DAIN

The voltage actually fed to the LNB is divided down & connected here (feedback) for the on-chip regulator.

#### IV - SOUND DETECTION BLOCK

The different de-emphasis formats are selected through the audio MUX and are the same for both channels. That is, as with the volume control, the I<sup>2</sup>C bus registers simultaneously control both channels with each bit of registers.

#### Pin 16 AUXIN1

This pin allows an auxilliary audio signal to be connected to the input of channel 1 audio processor and hence makes use of the on chip filters, ANRS, mux and volume control. An on-board MAC decoder is a typical user of this feature.

#### Pin 17 U751

A capacitor and resistor in parallel of 75 $\mu$ s time constant connected between here and V<sub>REF</sub> (Pin 27) to provide 75 $\mu$ s de-emphasis for channel 1. Internally selectable is an internal resistor that can be programmed to be added in parallel thereby converting the network to approx 50 $\mu$ s de-emphasis. The value of the internal resistor is 44k $\Omega$   $\pm$  30%. The amplifier for this filter is voltage input, current output; with  $\pm$  500mV input the output will be  $\pm$  55 $\mu$ A.

# Pin 18 J171

The external J17 de-emphasis network for channel 1. The amplifier for this filter is voltage input, current output; with  $\pm$  500mV input the output will be  $\pm$  55 $\mu$ A.

# Pin 19 AUXIN2

This pin allows an auxilliary audio signal to be connected to the input of channel 2 audio processor and hence makes use of the on-chip filters, ANRS, MUX and volume control. An on-board MAC decoder is a typical user of this feature.

#### Pin 20 U752

A capacitor and resistor in parallel of 75 $\mu$ s time constant connect between here and V<sub>REF</sub> (Pin 27) to provide 75 $\mu$ s de-emphasis for channel 2. Internally selectable is an internal resistor that can be programmed to be added in parallel thereby converting the network to approx 50 $\mu$ s de-emphasis (see control block map). The value of the internal resistor is 44 $\mu$ c ± 30%. The amplifier for this filter is voltage input, current output; with  $\pm$  500mV input the output will be  $\pm$  55 $\mu$ A.

#### Pin 21 J172

The external J17 de-emphasis network for channel 2. The amplifier for this filter is voltage input, output current. Output with  $\pm$  500mV input will be  $\pm$  55 $\mu A.$

# Pin 22 GND

This ground pin is double bonded; 1) to channel 1 RF section & VCO and 2) to both AGC amplifiers, channel 1 audio section, audio MUX, internal power & references to audio section.

#### Pin 23 DET1

The output of FM phase detector 1 (left channel). This is for the connection of an external loop filter for the PLL. The output is a push pull current source with  $\pm~90\mu A$  output with  $\pm~500mV$  input to the internal mixer.

#### Pin 24 FMIN1

This is the +ve input to the two FM demodulators. It feeds two AGC amplifiers with a bandwidth of at least 5-10MHz. There is one amplifier for each channel both with the same differential input. The AGC amplifiers have a 0dB to + 40dB range and will produce a constant signal of 1.0V about the 2.44V reference into the respective demodulators.

$Z_{IN} = 5k\Omega$  Min input =  $2mV_{PP}$  per subcarrier Max input =  $500mV_{PP}$  (max when all inputs are added together, when their phases coincide).

#### Pin 25 AGC1

AGC amplifier 1 peak detector capacitor connection. The output current has an attack/decay ratio of 1:32. That is the ramp up current is approximately  $5\mu A$  and decay current is approximately  $160\mu A$ . 11V gives maximum gain. This pin is also driven by a circuit monitoring the voltage on AM-PLOCK1.

#### Pin 26 FMIN2

This is the -ve input to the AGC amplifiers forming a differential input stage. All inputs are biased to  $V_{REF}$  (2.44V) via an internal  $10k\Omega$  resistor.

# Pin 27 VREF (2.44V)

This is the audio processor voltage reference used throughout the FM/audio section of the chip. As such it is essential that it is well decoupled to ground to reduce as far as possible the risk of crosstalk and noise injection. This voltage is derived directly from the bandgap reference of 1.22 volts.

# Pin 28 V<sub>CC</sub> (+12V power supply)

Double bonded main power pin for the audio/FM section of the chip. The two bond connections are:

- 1) to the ESD and guard rings and

- to power the circuit and on chip regulators/references.

#### Pin 29 DET2

The output of FM phase detector 2 (right channel). This for the connection of an external loop filter for the PLL. The output is a push-pull current source with  $\pm$  90mA output with  $\pm$  500mV input to the internal mixer. See pin 23.

#### Pin 30 AMPLOCK1

The output of amplitude detector 1. Requires a capacitor and a resistor to GND. The voltage across this is used to decide whether there is a signal being received by FM det 1. The level detector output drives a bit in the 'control block' I<sup>2</sup>C bus register 7 bit 0. This also drives AGC amp 1. When the voltage on this pin is >(V<sub>REF</sub>+1V<sub>BE</sub>) it sinks current to V<sub>REF</sub> from Pin 25 to reduce the AGC gain.

#### Pin 31 CPUMP1

The output from the frequency synthesiser is a push-pull current source which requires a capacitor to ground to derive a voltage to pull the VCO to the target frequency. The output is  $\pm$  100 $\mu A$  to achieve lock and  $\pm$  2 $\mu A$  during lock to provide a tracking time constant of approximately 10Hz.

#### Pin 32 AGC2

AGC amplifier 2 peak detector capacitor connection. The output current has an attack/decay ratio of 1:32. That is the ramp up current is approximately  $5\mu A$  and decay current is approximately  $160\mu A$ . 11V gives maximum gain. This pin is also driven by a circuit monitoring the voltage on AM-PLOCK2.

#### Pin 33 GND

This ground pin is double bonded; 1) to the volume control, ANRS, ESD and guard rings and 2) to the VCO & RF section of channel 2.

# Pin 34 AMPLOCK2

The output of amplitude detector 2. Requires a capacitor and resistor to GND. The voltage across this is used to decide whether there is a signal being received by FM det 2. The level detector output drives a bit in the 'control block'  $I^2C$  bus register 7 bit 1. This also drives AGC amp 2. When the voltage on this pin is  $>(V_{REF}+1V_{BE})$  it sinks current to  $V_{REF}$  from Pin 32 to reduce the AGC gain.

#### Pin 35 CPUMP2

The output from the frequency synthesiser is a push-pull current source which requires a capacitor to ground to derive a voltage to pull the VCO to the target frequency. The output is  $\pm$  100 $\mu A$  to achieve lock and  $\pm$  2 $\mu A$  during lock to provide a tracking time constant of approximately 10Hz.

#### Pin 36 IREF

This is a buffered  $V_{REF}$  output to an off-chip resistor to produce an accurate current reference, within the chip, for the biasing of amplifiers with current outputs into filters. It is also required for the ANRS circuit to provide accurate rolloff frequencies. This

pin should not be decoupled as it will inject current noise. The target current is  $10\mu A\pm 2$  thus a  $240k\Omega\pm 1\%$  is required.

# V - AUTOMATIC NOISE REDUCTION SYSTEM (ANRS) AND VOLUME CONTROL

There is a ANRS defeat which allows the audio to bypass the ANRS section but still go to the volume control. The volume control will be 32 steps of 1.25dB, with the lowest step being audio 'mute' (no output).

#### Pin 37 PEAKOUT

The ANRS control loop peak detector output requires a capacitor to ground from this pin. Also a  $1.2 M\Omega$  resistor to  $V_{REF}$  Pin 27 to give some accurate decaytime constant. The value of the capacitor and resistor control the attack and decay times, typically 0.1 ms attack & 25 ms decay.

#### Pin 38 FCLEFT

The variable bandwidth gm amplifier has a current output which is variable depending on the input signal amplitude as defined by the control loop. The output current is then dumped into an off-chip capacitor which together with the accurate current reference define the min/max rolloff frequencies. A 330pF capacitor is connected to ground from this pin for channel 1 (left).

#### Pin 39 PEAKIN

This is the input to the control loop peak detector and is connected to the output of the off-chip control loop band pass filter. This requires AC coupling between this input pin and the summer output Pin 40.

#### Pin 40 SUMOUT

The two audio inputs are summed together with an amplifier with a gain of 0.5 ie. if both inputs are 1 volt then the output is 1 volt. This amplifier has an input follower buffer which gives a  $V_{BE}$  offset in the DC bias voltage. Thus the filter which this amplifier drives must include AC coupling to the next stage (Pin 39).

#### Pin 41 FCRIGHT

The variable bandwidth gm amplifier has a current output which is variable depending on the input signal amplitude as defined by the control loop. The output current is then dumped into an off-chip capacitor which together with the accurate current reference define the min/max rolloff frequencies. A 330pF capacitor is connected to ground from this pin for channel 2 (right).

#### Pin 42 AUDIOOUT2

The main audio output from the volume control level shifted and amplified to produce  $2V_{PP}$  on a DC bias of 4.88 volts. This amplifier has short circuit protection and is intended to drive a SCART connector directly via AC coupling and meets the standard SCART drive requirements. This pin is the channel 1 or left output.

#### Pin 43 AUDIOOUT1

The main audio output from the volume control level shifted and amplified to produce  $2V_{PP}$  on a DC bias of 4.88 volts. This amplifier has short circuit protection and is intended to drive a SCART connector directly via AC coupling and meets the standard SCART drive requirements. This pin is the channel 2 or right output.

#### VI - VIDEO BLOCK

#### Pin 45 S2VIDIN

External video input  $1V_{PP}$  AC coupled  $75\Omega$  source impedance returned from a VCR for example. This input has a DC restoration clamp on its input. This gets the video to the correct DC level so that OSD can be added later when it is essential that the voltages of the video and OSD are at the correct levels with respect to each other. The clamp sink current is  $1\mu A \pm 30\%$  with the buffer  $Z_I > 1M\Omega$ . This signal is an input to the Video Matrix and is called SCART-2 Return.

#### Pin 46 S1VIDIN

External video input 1.0 V<sub>PP</sub> AC coupled  $75\Omega$  source impedance. This input has a DC restoration clamp on its input. This gets the video to the correct DC level so that OSD can be added later when it is essential that the voltages of the video and OSD are at the correct levels with respect to each other. The clamp sink current is  $1\mu A \pm 30\%$  with the buffer  $Z_{IN} > 1M\Omega$ . This signal is an input to the Video Matrix and is called SCART-1 Return.

#### Pin 47 DEC1IN

This input receives a PAL encoded output from, for instance a D2MAC decoder inside the receiver. The signals from Pins 47 and 48 go to an internal selector switch that selects which signal goes to the Video Matrix.

#### Control bit

1 bit I<sup>2</sup>C bus Reg 1 bit 4 Signal selected default --- 0 Pin 48 (DEC2IN) 1 Pin 47 (DEC1IN)

The output signal from the selector switch, which goes to the Video Matrix, is called Internal Decoder Return.

#### Pin 48 DEC2IN

This input can be driven for instance by the output of a Videocrypt decoder  $Z_{OUT} = 500\Omega$  video about  $1.0 V_{PP}$  from the reconstruction filter. This input has a DC restoration clamp on its input. This gets the video to the correct DC level so that OSD can be added later when it is essential that the voltages of the video and OSD are at the correct levels with respect to each other.

The clamp sink current is  $1\mu A\pm 30\%$  with the buffer  $Z_{IN} > 1M\Omega$ . The signals from Pins 47 and 48 go to an internal selector switch that selects which signal goes to the Video Matrix.

#### Control bit

1 bit Reg 1 bit 4 Signal selected default --- 0 Pin 48 (DEC2IN) 1 Pin 47 (DEC1IN)

### Pin 49 SYNCIN

This input can be programmed to accept either a digital or an analog sync stream. The digital input will accept a made up sync signal consisting of the Genlock 'line' and 'frame' sync output. If it is smaller than 0.8V then it produces a sync tip level voltage (1.22V). If it is greater than 2.0V it produces black level (1.52V). This will generate a sync stream signal consisting of syncs only, that will be available on the 'Video Matrix'. The DC level of these syncs at the SCART O/Ps will be sync tip = 1.22V black level = 1.82V.

The analogue path is effectively just like another video input source, additionally you can decide whether to clamp this input. Doing this will allow you to put an analogue sync stream into the unit. This could then contain an overall background brightness for the screen (this cannot be done by simply making the black level clamps would be upset).

#### Control bits

2 bits I<sup>2</sup>C bus Reg 1 bits 6 ,5 Effect

Sync source

default ----- X 0 Digital

0 1 Analog

1 1 Analog clamped

#### Pin 50 OSDIN

Typically driven by a combination of an OSD O/P and the 'Blank' output from the OSD bit of the Micro. This input is then threshold detected and two outputs are generated.

| Input    | Outp       | ut   |  |

|----------|------------|------|--|

|          | Background | Text |  |

| < 0.8V   | Ō          | 0    |  |

| 1.5-2.5V | 1          | 0    |  |

| > 3.5V   | 1          | 1    |  |

#### Pin 51 S3VIDOUT

Video driver for SCART-3 with OSD. This requires an external emitter follower buffer to drive a  $150\Omega$  load. The average DC voltage to be 1.5V on the O/P. The signal on Pin 51 is video  $2.0V_{PP}$  5.5MHz B/W with sync tip=1.22V. This SCART O/P will be used to drive the TV typically. This pin gets its signal from the Video Matrix. It is then amplified and OSD is added before being output. The signal selected from the Video Matrix for output on this pin is controlled by a control register.

# Control bits

3

| bits I <sup>2</sup> C bus Reg 4 bits | 3 2, | 1, | 0 | Source selected  |

|--------------------------------------|------|----|---|------------------|

|                                      | 0    | 0  | 0 | Baseband         |

|                                      | 0    | 0  | 1 | De-emphasised    |

|                                      | 0    | 1  | 0 | Normal video     |

| default                              | 0    | 1  | 1 | Decoder return   |

|                                      | 1    | 0  | 0 | SCART 1 return   |

|                                      | 1    | 0  | 1 | SCART 2 return   |

|                                      | 1    | 1  | 0 | Syncs            |

|                                      | 1    | 1  | 1 | Nothing selected |

|                                      |      |    |   |                  |

OSD addition is controlled by a control register. It is possible to separately control whether or not to add 'blanking' and/or 'text' to the video stream to this SCART output.

# Control bits

| 2 bits I <sup>2</sup> C bus Reg 4 bits | 4, | 3      | Effect enabled                                            |

|----------------------------------------|----|--------|-----------------------------------------------------------|

| default                                | 0  | 0<br>1 | Background = Off Text = Off<br>Background = On Text = Off |

|                                        | 1  | 0      | Background = Off Text = On                                |

|                                        | 1  | 1      | Background = $On Text = On$                               |

#### Pin 52 S2VIDOUT

(See 1/ SCART drivers with OSD). Video driver for SCART-2. See Pin 51.

### Control bits

| 3 bits I <sup>2</sup> C bus Reg 3 bits | 2, | 1, | 0 | Source selected  |

|----------------------------------------|----|----|---|------------------|

|                                        | 0  | 0  | 0 | Baseband         |

|                                        | 0  | Ü  | 1 | De-emphasised    |

|                                        | 0  | 1  | 0 | Normal video     |

| default                                | 0  | 1  | 1 | Decoder return   |

|                                        | 1  | 0  | 0 | SCART 1 return   |

|                                        | 1  | 0  | 1 | SCART 2 return   |

|                                        | 1  | 1  | 0 | Syncs            |

|                                        | 1  | 1  | 1 | Nothing selected |

OSD addition is controlled by a control register. It is possible to separately control whether or not to add 'blanking' and/or 'text' to the video stream to this SCART output.

# Control bits

| 2 bits I <sup>2</sup> C bus Reg 3 bits | 4, | 3 | Effect enabled              |

|----------------------------------------|----|---|-----------------------------|

| default                                | 0  | 0 | Background = Off Text = Off |

|                                        | 0  | 1 | Background = On Text = Off  |

|                                        | 1  | 0 | Background = Off Text = On  |

|                                        | 1  | 1 | Background = On Text = On   |

See also Pin 5 where it is possible to add sync to stabilise OSD or video.

#### Pin 53 S1VIDOUT

Video driver for SCART 1. See Pin 51. No OSD available on this output.

#### Control bits

| sed<br>rn<br>urn |

|------------------|

| urn              |

|                  |

| cted             |

| l                |

#### Pin 54 DECOUT2

Drives a second decoder such as D2MAC and this is able to pass 10MHz. See Pin 53.

# Control bits

| 3 bits I <sup>2</sup> C bus Reg 6 bits | 2,                         | 1,                         | 0                          | Source selected                                                                        |

|----------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------------------------------------------------------------------|

| default                                | 0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | Baseband De-emphasised Normal video Decoder return SCART 1 return SCART 2 return Syncs |

|                                        | 1                          | 1                          | 1                          | Nothing selected                                                                       |

# Pin 55 DECOUT1

This output can drive for instance a decoder. To allow for D2MAC it is able to pass 10MHz ;  $Z_{OUT}$  <  $75\Omega$ . Video on this pin will be  $1.9V_{PP} \pm 0.05V$ . When a Videocrypt encoded signal is output to the decoder on this pin its sync tips must be at  $1.49V_{DC} \pm 0.05V$ . This pin gets its signal from the Video Matrix. It is then level shifted and amplified by 1.9 before being output. The signal selected from the Video Matrix for output on this pin is controlled by a control register.

# Control bits

| 3 bits I <sup>2</sup> C bus Reg 5 bits | 2,  | 1, | 0 | Source selected  |

|----------------------------------------|-----|----|---|------------------|

|                                        | 0   | 0  | 0 | Baseband         |

|                                        | 0   | 0  | 1 | De-emphasised    |

|                                        | 0   | 1  | 0 | Normal video     |

| default                                | - 0 | 1  | 1 | Decoder return   |

|                                        | 1   | 0  | 0 | SCART 1 return   |

|                                        | 1   | 0  | 1 | SCART 2 return   |

|                                        | 1   | 1  | 0 | Syncs            |

|                                        | 1   | 1  | 1 | Nothing selected |

# Pin 56 V<sub>CC</sub>

+12V double bonded; 1) ESD+guard rings & 2) video circuit power.

# Pin 57 GND

Strategically placed video power ground connection to reduce video currents getting into rest of circuitry.

#### Pin 58 CLAMPIN

This pin clamps the most negative extreme of the input (the sync tips) to +1.22V<sub>DC</sub> (or appropriate voltage). The video at the clamp input is only 1V<sub>PP</sub>. This clamped video which is de-emphasised, filtered and clamped (energy dispersal removed) is normal, negative syncs, video. This signal drives the Video Matrix input called Normal Video.

It has a weak (1.0 $\mu$ ű 15%) stable current source pulling the input towards GND. Otherwise the input impedance is very high at DC to 1kHz  $Z_{IN} > 2M\Omega$ . Video bandwidth through this is -1dB at 5.5MHz. The CLAMP input DC restore voltage is then used as a means for getting the correct DC voltage on the SCART outputs.

#### Pin 59 DEEMPHOUT

Output of de-emphasis ZOUT <  $50\Omega$  2V<sub>PP</sub> B/W still 10.25MHz. This is the output that drives the capacitor into the CLAMP. It has to do this via the sound removal filter which may be a 5 or 7 pole low pass filter  $Z_{IN} = Z_{OUT} = 500\Omega$  -3dB corner about 5.25MHz. Video at pin 59 is positive. Internally the 2V<sub>PP</sub> video is reduced to 1V<sub>PP</sub> to drive the internal Video Matrix input called De-emphasised video. This signal also called 'Unclamped Unfiltered' and is the signal required by Filmnet PAL decoders for example. It is called unfiltered because it still has its high frequency sub-carriers (not been through the low pass filter).

# Pin 60 DEEMPHIN

Input of de-emphasis stage, with a  $Z_{IN}$  of  $10k\Omega$  or greater. B/W is 10.25MHz. The network between pins 59 & 60 will give 2x gain at 1.52MHz, about -2dB gain at 5MHz and +17dB gain at 10kHz as in accordance with CCIR 405-1.

#### Pin 61 VIDIN

AC-coupled Video input from a tuner. This is raw baseband up to 10.25MHz. Input amplitude is 0.25 - 1.0VPP at 1.52MHz.  $Z_{IN} > 5k\Omega$ . This drives an on-chip video amplifier. The other input pin of this amp is AC grounded by being connected to an internal V<sub>REF</sub>. The video amplifier has selectable gain from 0dB to 7dB in 8 steps. This is program-

mable, as is the output selected, whether normal or inverted.

Control bits

The normal or inverted output selected (which is 1.0V<sub>PP</sub>) also drives the Video Matrix input called Baseband.

Control bit

#### Pin 62 GND

Ground, especially for the low level input from the tuner.

#### VII - CLOCK - ALARM/TIMER

The real time clock has an alarm function.

The target alarm time is loaded into registers 21, 21 and 23 with bit 5 of reg 16 having been selected, and comparing it with the mins, hours, days of registers 18, 19 and 20, which form the real time clock. When the alarm condition is achieved bit 6 of I<sup>2</sup>C register 18 is set high. This must then be read periodically by the micro to see if an alarm has been reached. The range of the timer is 512 days in one minute steps.

#### **VIII - STANDBY**

This chip does NOT have a standby mode. The Internal power on reset will reset the default status of the chip, if either power rail is removed or reduced after the power returns to a good staus. Thus the controlling microprocessor will have to remenber any current operating conditions.

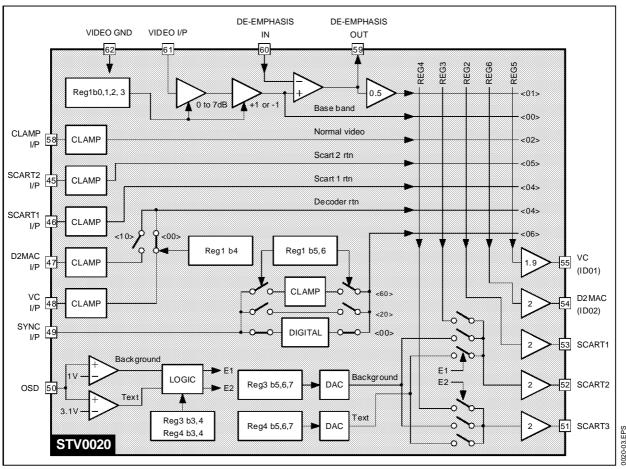

Figure 1: Fundamental Block Diagram

Figure 2: Video Processing Block Diagram

**CHANNEL 1** Det | Cpump Reg 05 b3,4 Reg 06 b5 AUDIO 1 <60> Mod Depth 0.25 to 1 LEVEL bias DETECTOR 1 AGC <18> Reg 06 b3 V<sub>REF</sub> LEVEL DETECTOR 2 AMP LOCK1 VCO 0 1/1000 FREQUENCY PHASE **MEASURE** СОМРО 100ms  $V_{REF}$ Reg 0C,0D 10kHz Reg 07 b0 Reg 08,09 STV0020 CHANNEL 2 Cpump Reg 05 b3,4 Reg 06 b6 AUDIO2 24 <60> Mod Depth 0.25 to 1 <18> LEVEL bias **DETECTOR 1** AGC <18> Reg 06 b4 ■ V<sub>REF</sub> LEVEL DETECTOR 2 90 VCO AMP LOCK2 30 1/1000

Figure 3: FM Demodulation Block Diagram

Reg 0A,0B

PHASE

COMPO

10kHz

100 ₩

FREQUENCY

**MEASURE**

Reg 0E,0F

Gate

100ms

Reg 07 b1

VREF

STV0020

0020-04A.EPS - 0020-04B.EPS

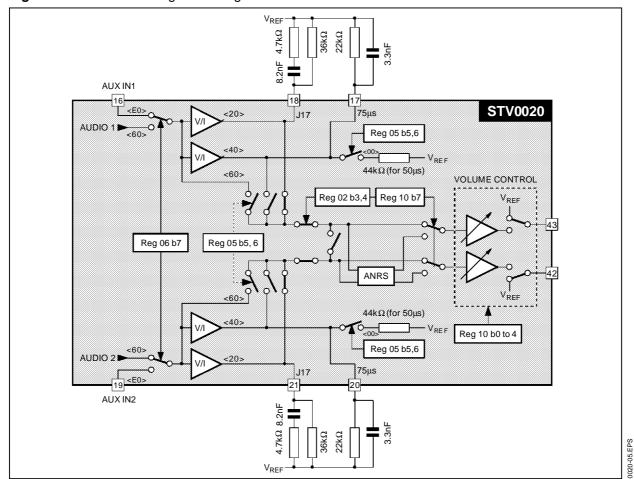

Figure 4: Audio Processing Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                 | Parameter                   | Value       | Units |

|------------------------|-----------------------------|-------------|-------|

| Vcc<br>V <sub>DD</sub> | Supply voltage              | 13.2<br>7.0 | V     |

| P <sub>tot</sub>       | Total power dissipation     | 1.0         | W     |

| T <sub>oper</sub>      | Operating temperature range | 0, +70      | °C    |

| T <sub>stg</sub>       | Storage temperature         | -55, +150   | °C    |

# **THERMAL DATA**

| Symbol               | Parameter                           | Value | Unit |

|----------------------|-------------------------------------|-------|------|

| R <sub>th(j-a)</sub> | Thermal resistance junction-ambient | 60    | °C/W |

# DC AND AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 12V, V<sub>DD</sub> = 5V, T<sub>amb</sub> = 25°C unless otherwise specified)

| Symbol                               | Parameter            | Test Conditions | Min.         | Тур.      | Max.         | Unit     |          |

|--------------------------------------|----------------------|-----------------|--------------|-----------|--------------|----------|----------|

| V <sub>CC</sub><br>V <sub>DD</sub>   | Supply voltage range |                 | 11.5<br>4.75 | 12<br>5.0 | 12.5<br>5.25 | V        | ] [      |

| IQ <sub>cc</sub><br>IQ <sub>dd</sub> | Supply current       |                 |              | 55<br>8   | 70<br>15     | mA<br>mA | 0020-05. |

DC AND AC ELECTRICAL CHARACTERISTICS (continued)  $(V_{CC} = 12V, V_{DD} = 5V, T_{amb} = 25^{\circ}C$  unless otherwise specified)

| -        |                                                                |                                                                         |      |      |      |                  |

|----------|----------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|------------------|

| Symbol   | mbol Parameter Test Condition s                                |                                                                         | Min. | Тур. | Max. | Unit             |

| AUDIO DE | EMODULATOR (see Figure 3)                                      |                                                                         |      |      |      |                  |

| FMI      | FM Subcarrier Input Level<br>Pin 24 - Pin 26 for AGC Action    | VCO locked on carrier at 6MHz, 680kΩ load on Pin 30 and Pin 34          | 5    |      | 500  | mV <sub>PP</sub> |

| DETH     | Detector 1 and 2 (Pins 30 and 34) threshold for activating AGC |                                                                         |      | 3.1  |      | V                |

| IDETA    | Max Sink/Source Pins 30 and 34 Current                         | With AGC operation                                                      |      | 100  |      | μΑ               |

| IDETS    | Max Sink/Source Pins 30 and 34 Current                         | Without AGC limited gain                                                |      | 200  |      | μА               |

| VCOMI    | VCO Mini Frequency                                             | V <sub>CC</sub> : 11.5 to 12.5V, T <sub>amb</sub> : 0 to 70°C           |      |      | 5    | MHz              |

| VCOMA    | VCO Maxi Frequency                                             | V <sub>CC</sub> : 11.5 to 12.5V, T <sub>amb</sub> : 0 to 70°C           | 8.6  |      |      | MHz              |

| AP50     | 1kHz Audio Level at PLL Output Pins 23 and 29                  | 0.5V <sub>PP</sub> 50kHz deviation FM input<br>Deviation set to 50kHz   | 0.5  | 0.85 | 1.5  | V <sub>PP</sub>  |

| AP100    | 1kHz Audio Level at PLL Output Pins 23 and 29                  | 0.5V <sub>PP</sub> 100kHz deviation FM input<br>Deviation set to 100kHz | 0.5  | 0.85 | 1.5  | V <sub>PP</sub>  |

| AP150    | 1kHz Audio Level at PLL Output Pins 23 and 29                  | 0.5V <sub>PP</sub> 150kHz deviation FM input<br>Deviation set to 150kHz | 0.5  | 0.85 | 1.5  | V <sub>PP</sub>  |

| AP200    | 1kHz Audio Level at PLL Output Pins 23 and 29                  | 0.5V <sub>PP</sub> 200kHz deviation FM input<br>Deviation set to 200kHz | 0.5  | 0.85 | 1.5  | V <sub>PP</sub>  |

| DPCO     | Digital Phase Comparator Pins 31 and 35 Output Current         | Sink and source current to external capacitor                           |      | 100  |      | μА               |

| AUDIO DE | E-EMPHASIS (1VPP at Audio Processor Inpu                       | it)                                                                     |      |      |      |                  |

| D50e     | 1kHz Audio Level on 50μs<br>De-emphasis Output Pins 17 and 20  | 22k $\Omega$ and 2.2nF load Internal 44k $\Omega$ off                   |      | 1.91 |      | V <sub>PP</sub>  |

| D50i     | 1kHz Audio Level on 50μs<br>De-emphasis Output Pins 17 and 20  | 22kΩ and 3.3nF load<br>Internal 44kΩ on                                 |      | 1.30 |      | V <sub>PP</sub>  |

| D75      | 1kHz Audio Level on 50μs<br>De-emphasis Output Pins 17 and 20  | 22kΩ and 3.3nF load Internal 44kΩ off                                   |      | 1.80 |      | V <sub>PP</sub>  |

| DJ17     | 1kHz Audio Level on J17<br>De-emphasis Output Pins 18 and 21   | Load as in Figure 3                                                     |      | 1.45 |      | V <sub>PP</sub>  |

| R50      | Internal Resistor for 50/75µs Switching                        |                                                                         | 30   | 44   | 58   | kΩ               |

| AUTOMAT  | TIC NOISE REDUCTION SYSTEM                                     |                                                                         |      | •    |      | •                |

| LRS      | Left + Right Summer Output Pin 40                              | 1V <sub>PP</sub> on left and right channel                              | 0.9  | 1    | 1.1  | V <sub>PP</sub>  |

| NDRT     | Pin 37 Level Detector Rise Time Constant                       | External 22nF load                                                      |      | 110  |      | μs               |

| NDFT     | Pin 37 Level Detector Fall Time Constant                       | External 22nF to GND and 1.2M $\Omega$ to Pin 27                        |      | 26.4 |      | ms               |

| NDLL     | Pin 37 Bias Level                                              | No audio in                                                             |      | 2.44 |      | V                |

| NDML     | Pin 37 Max Level (internal clamp)                              | 3 V <sub>PP</sub> 1kHz on Pins 23 and 29                                | 2.7  | 3    | 3.2  | V                |

| LLCF     | Noise Reduction Cutoff Frequency for Low Level Audio           | 100mV <sub>PP</sub> on Pins 23 and 29                                   |      | 0.85 |      | kHz              |

| HLCF     | Noise Reduction Cutoff Frequency at High Level                 | 1 V <sub>PP</sub> on Pins 23 and 29                                     |      | 7    |      | kHz              |

|          |                                                                |                                                                         |      |      |      |                  |

DC AND AC ELECTRICAL CHARACTERISTICS (continued)  $(V_{CC} = 12V, V_{DD} = 5V, T_{amb} = 25^{\circ}C$  unless otherwise specified)

| Symbol          | Parameter                                                                                        | Test Conditions                                                            | Min. | Тур. | Max. | Unit            |

|-----------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|-----------------|

| AUDIO OU        | TPUT (Pins 42 and 43)                                                                            |                                                                            |      |      |      | •               |

| DCOL            | DC Output Level<br>measured on Pins 42 and 43                                                    | Aux input Pins 16 and 19 connected to V <sub>REF</sub>                     |      | 4.7  |      | V               |

| AOLN            | Audio Output Level at Nominal Input at 0dB<br>Attenuation Setting, measured on Pins 42<br>and 43 | FM input as for AP50<br>No de-emphasis<br>No noise reduction               | 0.9  | 1.6  | 2.85 | V <sub>PP</sub> |

| AOL50           | Audio Output Level at Nominal Input at 0dB<br>Attenuation Setting, Measured on Pins 42<br>and 43 | FM input as for AP50<br>50µs de-emphasis as for D50i<br>No noise reduction |      | 2.1  |      | V <sub>PP</sub> |

| AOL17           | Audio Output Level at Nominal Input at 0dB<br>Attenuation Setting, Measured on Pins 42<br>and 43 | FM input as for AP50,<br>J17 de-emphasis<br>No noise reduction             |      | 2.4  |      | V <sub>PP</sub> |

| AMA1            | Audio Output Attenuation with Mute On                                                            | 1V <sub>PP</sub> - 1kHz, from Aux input<br>Pins 16, 19 to Pins 42, 43      |      | 60   |      | dB              |

| MXAT            | Max Attenuation before Mute                                                                      | 1kHz, from Aux input Pins 16<br>and 19 to Pins 42 and 43                   | 31.7 | 32.7 | 33.7 | dB              |

| MXAG            | Max Audio Gain                                                                                   | 1kHz, from Aux input Pins 16 and 19 to Pins 42 and 43                      |      | 1.9  |      |                 |

| ASTP            | Attenuation of each of the 31 steps                                                              | 1kHz                                                                       |      | 1.25 |      | dB              |

| THDA1           | THD at 0dB Attenuation Setting                                                                   | 1V <sub>PP</sub> - 1kHz, from Aux input<br>Pins 16, 19 to Pins 42, 43      |      | 0.15 |      | %               |

| THDAUX          | THD at 0dB Attenuation Setting                                                                   | 2V <sub>PP</sub> - 1kHz, from Aux input<br>Pins 16, 19 to Pins 42, 43      |      | 0.4  | 1    | %               |

| THDFM           | THD at 0dB Attenuation Setting                                                                   | FM input as for AP50<br>No de-emphasis, no ANRS                            |      | 0.4  | 2    | %               |

| ACS             | Audio Channel Separation measured on Pins 42, 43                                                 | 1V <sub>PP</sub> - 1kHz on Aux input<br>Pins 16, 19                        |      | 80   |      | dB              |

| SNFM            | Signal to Noise Ratio measured on Pins 42, 43                                                    | FM input as for AP50<br>50μs de-emphasis, no ANRS                          |      | 62   |      | dBA             |

| SNFMNR          | Signal to Noise Ratio measured on Pins 42, 43                                                    | FM input as for AP50<br>No de-emphasis, ANRS is on                         |      | 80   |      | dBA             |

| I/O's (Pins     | 2, 3, 4, 9 and 10)                                                                               |                                                                            |      |      |      |                 |

| SCIL            | Pin 2, 3 or 4 Low Level Input                                                                    |                                                                            |      |      | 2    | V               |

| SCIH            | Pin 2, 3, or 4 High Level Input                                                                  |                                                                            | 9.5  |      |      | V               |

| SCOH            | Pin 2, 3 or 4 High Level Output                                                                  | 10kΩ load to ground                                                        | 9.5  | 11   |      | V               |

| SCOL            | Pin 2, 3 or 4 Low Level Output                                                                   | 10kΩ load to ground                                                        |      | 0.1  | 2    | V               |

| V <sub>IL</sub> | Pin 6, 7, 8, 9 or 10 Low Level Input                                                             |                                                                            |      |      | 0.8  | V               |

| V <sub>IH</sub> | Pin 6, 7, 8, 9 or 10 High Level Input                                                            |                                                                            | 2.4  |      |      | V               |

| V <sub>OL</sub> | Pin 6, 7, 8, 9 or 10 Low Level Output                                                            | I <sub>Sink</sub> = 2mA                                                    |      | 0.2  | 0.4  | V               |

| V <sub>OH</sub> | Pin 6, 7, 8, 9 or 10 High Level Output                                                           | I <sub>Source</sub> = 2mA                                                  | 3.2  | 4.6  |      | V               |

| RESET           |                                                                                                  |                                                                            |      |      |      |                 |

| RSR             | Reset iNternal Pull Up Resistor                                                                  | Reset high                                                                 |      | 10   |      | kΩ              |

| RSI             | Reset Internal Sink Current                                                                      | Reset low                                                                  |      | 2    |      | mA              |

| RTCCU           | End of Reset for V <sub>CC</sub>                                                                 | V <sub>DD</sub> = 5V, V <sub>CC</sub> going up                             |      | 9.2  |      | V               |

| RTCCD           | Start of Reset Threshold for V <sub>CC</sub>                                                     | V <sub>DD</sub> = 5V, V <sub>CC</sub> going down                           |      | 7.5  |      | V               |

| RTDDU           | End of Reset Threshold for V <sub>DD</sub>                                                       | $V_{CC}$ = 12V, $V_{DD}$ going up                                          |      | 3.8  |      | V               |

| RTDDD           | Start of Reset Threshold for V <sub>DD</sub>                                                     | Vcc = 12V, V <sub>DD</sub> going down                                      |      | 3.2  |      | V               |

DC AND AC ELECTRICAL CHARACTERISTICS (continued)  $(V_{CC} = 12V, V_{DD} = 5V, T_{amb} = 25^{\circ}C$  unless otherwise specified)

| Symbol   | Parameter                                                                                    | Test Conditions                                                                 | Min. | Тур. | Max. | Unit            |

|----------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|-----------------|

| D/A CONV | ERTER ref.: fig. 1                                                                           |                                                                                 |      |      |      |                 |

| DA00     | Minimum Output Voltage on Pin 15 for 00 hex                                                  | Sense input Pin 44 connected to output Pin 15 and 10kΩ load resistor to GND     | 0    | 30   | 60   | mV              |

| DAFF     | Max Output Voltage on Pin 15 for FF hex                                                      | as for DA00                                                                     | 2.15 | 2.35 | 2.55 | V               |

| ILE      | Integral Linearity                                                                           |                                                                                 |      | 0.5  | 2    | LSB             |

| COMPOSI  | TE SIGNAL PROCESSING (see Figure 2)                                                          |                                                                                 |      |      |      |                 |

| VIDC     | Pin 61 DC Level                                                                              | External load current < 1µA                                                     | 2.15 | 2.35 | 2.55 | V               |

| ZVI      | Pin 61 input impedance                                                                       |                                                                                 |      | 10   |      | kΩ              |

| DEODC    | Pin 59 DC Output Level                                                                       | 1.2kΩ from Pin 59 to Pin 60 and 2kΩ from Pin 60 to GND                          | 3.3  | 3.7  | 4.1  | V               |

| DEOAC    | Pin 59 AC Level for GV = 0 dB                                                                | Pin 61 level = 1V <sub>PP</sub> , 100kHz                                        | 1.87 | 2    | 2.13 | V <sub>PP</sub> |

| DEOMX    | Pin 59 Max AC Level Before Clipping                                                          | GV = 0 dB                                                                       | 5    | 6    |      | V <sub>PP</sub> |

| DEOISC   | Pin 59 Max Source Current                                                                    |                                                                                 |      | 8    |      | mA              |

| DEOISK   | Pin 59 Max Sink Current                                                                      |                                                                                 |      | 2    |      | mA              |

| ZDEO     | Pin 59 Output Impedance @ 5MHz                                                               |                                                                                 |      | 2    |      | Ω               |

| DGV      | Gain Error vs GV @ 100kHz                                                                    | For GV = 1, 2, 3, 4, 5, 6 or 7                                                  | -0.5 | 0    | 0.5  | dB              |

| DINV     | Gain Variation when using inverter                                                           | @ 100kHz                                                                        | -0.5 | 0    | 0.5  | dB              |

| DEBW     | Bandwidth at Pin 59 for 1V <sub>PP</sub> input measured on Pin 59                            | @ -3dB with GV = 0dB                                                            | 10   | 20   |      | MHz             |

| DFG      | Differential Gain On Sync Pulses<br>measured on Pin 59                                       | 1 V <sub>PP</sub> CVBS + 0.5V <sub>PP</sub> 25Hz<br>sawtooth input Pin 61, GV=0 |      |      | 1    | %               |

| CLAMP ST | AGES                                                                                         |                                                                                 |      |      |      |                 |

| ISKC     | Clamp Input Sink Current Pin 49 when programmed with clamp and Pins 45, 46, 47, 48 and 58    | V <sub>IN</sub> = 3V                                                            | 0.6  | 1    | 1.4  | μА              |

| ISCC     | Clamp Input Source Current Same Pins as ISKC                                                 | V <sub>IN</sub> = 2V                                                            | 30   | 50   | 70   | μА              |

| VCL      | Sync Tip Level On Selected Output Pin (Pins 51, 52, 53 or 54)                                | 1V <sub>PP</sub> CVBS through 10nF on input (45,46,47 or 58)                    | 1.1  | 1.22 | 1.34 | V               |

| VCL5     | Sync Tip Level On Pin 55                                                                     | Same as for VCL                                                                 | 1.38 | 1.46 | 1.54 | V               |

| VIDEO MA | TRIX                                                                                         |                                                                                 |      |      |      |                 |

| XTK      | Output level on any output when 1V <sub>PP</sub> CVBS input is selected for any other output | @ 5MHz                                                                          |      | 60   |      | dB              |

| BGT      | Background Graphics Threshold Pin 50                                                         |                                                                                 | 0.8  | 1    | 1.5  | V               |

| CGT      | Character Foreground Threshold Pin 50                                                        |                                                                                 | 2.5  | 3    | 3.5  | V               |

| BMN      | Background Level for 000 Selection                                                           | Measured on selected output<br>Pin 52 or 53                                     |      | 1.7  |      | V               |

| ВМХ      | Background Level for 111 Selection                                                           | Same as BMN                                                                     |      | 3.1  |      | V               |

| FMN      | Foreground Level for 000 Selection                                                           | Same as BMN                                                                     |      | 1.7  |      | V               |

| FMX      | Foreground Level for 111 Selection                                                           | Same as BMN                                                                     |      | 3.1  |      | V               |

| BFG      | Output Buffer Gain Pins 45,46,47,48,58                                                       | @ 100kHz                                                                        | 1.87 | 2    | 2.13 |                 |

| BFG5     | Output Buffer Gain Pin 55                                                                    | @ 100kHz                                                                        | 1.77 | 1.9  | 2.03 |                 |

#### CIRCUIT DESCRIPTION

#### I - Video Section

The composite video is first set to a standard level by means of a 8 step gain controlled amplifier. In the case that the modulation is negative, an inverter can be switched in. The deemphasis network is fed by a wide bandwidth amplifier and energy dispersal is removed by a sophisticated sync tip clamping circuit. This circuit is used on all inputs to a video switching matrix, thus making sure that no DC steps occur when switching video sources.

The matrix can be used to feed video to and from decoders such as D2MAC or scrambled analog video.

Two special inputs allow insertion of graphics on video or clean sync.

#### II - Audio Section

The two audio channels are totally independent except for the possibility given to output on both channels only one of the selected input audio channels

To allow a very cost effective application, each channel uses PLL demodulation. Except for the overall high pass filter removing the video of the composite signal, no complex filter is needed.

The frequency of the demodulated subcarrier is chosen by a frequency synthesiser which sets the frequency of the internal local oscillator by comparing its phase with the internally generated reference. When the frequency is reached, the microprocessor switches in the STV0020 PLL and the demodulation starts. At any moment the microprocessor can read from the device the actual frequency to which the PLL is locked. It can also verify that a carrier is present at the given frequency, thanks to an amplitude demodulator which is also used for the audio input AGC.

In order to maintain constant amplitude of the recovered audio regardless of variations between satellites or subcarriers, the PLL loop gain may be programmed from 4 values.

Two different networks can be permanently connected for either 75 $\mu s$  or J17 de-emphasis. If 50 $\mu s$  de-emphasis is required, this can be inserted by an internal switch, thus allowing a worldwide application.

A dynamic noise reduction system (ANRS) is used using a lowpass filter, the cutoff frequency of which is controlled by the amplitude of the audio after insertion of a bandpass filter.

One audio output is provided; it is a gain controlled  $2V_{PP}$ . This output is chosen by an audio matrix between non de-emphasised, 50 or  $75\mu s$  de-emphasised, J17 deemphasised audio channel. In each case the dynamic noise reduction system can be used. Alternatively the selected output can receive the auxilliary audio inputs. The gain controlled amplifier has a gain range from 0dB to -38.75dB with 1.25dB steps. This can also be muted.

The timer is effectively just a real time clock runing from the 4/8MHz crystal clock with a resolution of one miniute and range of 255 days. This is fully controllable via the IIC bus and any time can be set up to within one minute. Similarly the time can be read back very easily. Registers 18, 19 and 20 are used to store minutes hours and days respectively.

The intended use is for the time to be set in registers 18-20 as the real time and then compared perodically with a second time, the alarm time stored in registers 21, 22 and 23. When the two sets of registers are the same an alarm flag is set in register 22 bit 5. The alarm function can be switched on or off with bit 5 of register 16. The micro-controlle must actively check bit 5 of register 22 periodically to see if the alarm condition has been achieved.

The 8-bit Digital to Analog Converter outputs a voltage ranging from 0 and 2.44V via a differential amplifier for digital words from 00 to FF. By adding a suitable output buffer/converter, this DAC can be used to control LNB voltages (or polariser currents) with a range exceeding 0 to 2.44V.

#### **IIC CONTROL REGISTERS**

# Reg 1 IIC $\rightarrow$ reg

bit

- 0 L Select video gain (Pin 61, Vidin). LSB

- 1 L Select video gain (Pin 61, Vidin).

$0\to \text{+7dB}$

- 2 L Select video gain (Pin 61, Vidin). MSB

- 3 L Select video invert

- 4 L Select input from Pin 47 (Mac) or Pin 48 (Videocrypt) (L = 48 H = 47)

- 5 L Select sync source digital/analogue (Pin 49, syncin, H = analog)

- 6 L Select clamp off/on (Pin 49, H = clamp)

- 7 L Not used

# Reg 2 IIC $\rightarrow$ reg

bit

- 0 H Select source for SCART 1 O/P (Pin 53)

- 1 H Select source for SCART 1 O/P (Pin 53)

- 2 L Select source for SCART 1 O/P (Pin 53)

- 3 H Select Left/Right/Stereo

- 4 H Select Left/Right/Stereo

| 3 | 4 | Mux    |

|---|---|--------|

| Χ | 0 | left   |

| Х | 1 | right  |

| 0 | Χ | mono   |

| 1 | 1 | stereo |

- 5 L Test multiplex control VCOCLK1/Div1000 and Pin 4 (S1)

- 6 L Test multiplex control VCOCLK2/Div1000 and Pin 3 (S2)

- 7 L Test multiplex control RESET and Pin 2 (S3)

# $\textbf{Reg 3} \quad \textbf{IIC} \rightarrow \textbf{reg}$

bit

- 0 H Select source for SCART 2 O/P (Pin 52)

- 1 H Select source for SCART 2 O/P (Pin 52)

- 2 L Select source for SCART 2 O/P (Pin 52)

- 3 L Select OSD effect for SCART 2 (Background)

- 4 L Select OSD effect for SCART 2 (Text)

- 5 L Select OSD "background" level (LSB)

- 6 L Select OSD "background" level

- 7 L Select OSD "background" level (MSB)

# $\textbf{Reg 4} \quad \textbf{IIC} \rightarrow \textbf{reg}$

bit

- 0 H Select source for SCART 3 O/P (Pin 51)

- 1 H Select source for SCART 3 O/P (Pin 51)

- 2 L Select source for SCART 3 O/P (Pin 51)

- 3 L Select OSD effect for SCART 3 O/P (Pin 51) (Background)

- 4 L Select OSD effect for SCART 3 O/P (Pin 51) (Text)

- 5 H Select OSD "Text" level (LSB)

- 6 H Select OSD "Text" level

- 7 H Select OSD "Text" level (MSB)

# Reg 5 IIC $\rightarrow$ reg

bit

0 H Select source for decoder 1 O/P (Pin 55)

1 H Select source for decoder 1 O/P (Pin 55)

2 L Select source for decoder 1 O/P (Pin 55)

3 L Select audio detector gain (bandwidth/deviation of FM)

4 L Select audio detector gain (bandwidth/deviation of FM)

5 H Select de-emphasis

6 L Select de-emphasis

7 ? Not used

| 4 | 3 | Deviation |

|---|---|-----------|

| 0 | 0 | 50kHz     |

| 0 | 1 | 100kHz    |

| 1 | 0 | 150kHz    |

| 1 | 1 | 200kHz    |

| 5 | 6 | De-emphasis         |

|---|---|---------------------|

| 0 | 0 | 50μs<br>75μs<br>J17 |

| 0 | 1 | 75µs                |

| 1 | 0 | J17                 |

| 1 | 1 | none                |

Note: These 4 bits must be on the same register so that

they are written to at same time.

# Reg 6 IIC $\rightarrow$ reg

bit

0 H Select source for decoder 2 O/P (Pin 54)

1 H Select source for decoder 2 O/P (Pin 54)

2 L Select source for decoder 2 O/P (Pin 54)

3 H Select frequency synth 1 OFF/ON (L=OFF)

4 H Select frequency synth 2 OFF/ON (L=OFF)

5 L Select RF source OFF/ON to FM Det 1

6 L Select RF source OFF/ON to FM Det 2

7 L Select aux audio inputs (Pin 16, 19) to the audio processor - H = aux inputs, L = internal PLL

#### Reg 7 Reg $\rightarrow$ IIC

bit

0 Status of Amp\_lock 1

1 Status of Amp\_lock 2

2 GND

3 GND

4 GND

5 GND

6 GND

7 GND

# Reg 8 IIC $\rightarrow$ reg

bit

0 L Select data direction for I/O 1 (Pin 6) (H = outputs)

1 L Select data direction for I/O 2 (Pin 7) (H = outputs)

2 L Select data direction for I/O 3 (Pin 8) (H = outputs)

3 L Select data direction for I/O 4 (Pin 9) (H = outputs)

4 L Select data direction for I/O 5 (Pin 10) (H = outputs)

5 L Not used

6 L Select frequency for det 1. LSB (bit 0) of 10 bit value

7 H Select frequency for det 1.

```

Reg 9 IIC \rightarrow reg

bit

Select frequency for det 1, Note: bit 3 of 10 bit value

0

Н

Н

Select frequency for det 1.

1

2

Н

Select frequency for det 1.

3

H Select frequency for det 1.

L

Select frequency for det 1.

5

H Select frequency for det 1.

6

L

Select frequency for det 1.

7

Н

Select frequency for det 1 bit 9, MSB (10th bit) of 10 bit value

Reg 10 IIC \rightarrow reg

bit

0

Select data direction for S1 (Pin 4) (L = input state)

Select data direction for S2 (Pin 3) (L = input state)

2

Select data direction for S3 (Pin 2) (L = input state)

3

Text mux control for LD1 (lock detect channel 1) and Pin 6 (IO1)

4

L

Text mux control for LD2 (lock detect channel 2) and Pin 7 (IO2)

5

?

Not used

6

L

Select frequency for det 2, LSB (bit 0) of 10 bit value

7

Select frequency for det 2

Reg 11 IIC \rightarrow reg

bit

0

L

Select frequency for det 2, Note: bit 3 of 10 bit value

Select frequency for det 2

1

L

2

Select frequency for det 2

Н

3

Select frequency for det 2

4

Select frequency for det 2

5

Н

Select frequency for det 2

6

Select frequency for det 2

L

Select frequency for det bit 9, MSB (10th bit) of 10 bit value

Reg 12 IIC → reg (read/write), Note: bits 6, 7 are Read only

bit

Select/Status of I/O 1 (Pin 6)

0

L

1

L

Select/Status of I/O 2 (Pin 7)

2

Select/Status of I/O 3 (Pin 8)

3

L

Select/Status of I/O 4 (Pin 9)

4

L

Select/Status of I/O 5 (Pin 10)

5

Not used

6

Read frequency of watchdog 1, LSB (bit 0) of 10 bit value

7

Read frequency of watchdog 1

Reg 13 Reg → IIC (The watchdog is the vco frequency monitor)

bit

0

Read frequency of watchdog 1, Note: bit 3 of 10 bit value.

1

Read frequency of watchdog 1

2

Read frequency of watchdog 1

3

Read frequency of watchdog 1

4

Read frequency of watchdog 1

5

Read frequency of watchdog 1

6

```

Read frequency of watchdog 1

Read frequency of watchdog 1 bit 9, MSB (10th bit) of 10 bit value.

7

```

Reg 14 IIC \rightarrow reg (read/write,) Note: bits 6, 7 are Read only

bit

0

Select/Status of S1 (Pin 4)

L

Select/Status of S1 (Pin 3)

1

L

2

L

Select/Status of S1 (Pin 2)

3

Not used

Not used

5

Not used

6

Read frequency of watchdog 2. Note: - bit 0 of 10 bit value

7

Read frequency of watchdog 2.

Reg 15 Reg → IIC (The watchdog is the vco frequency monitor)

bit

0

Read frequency of watchdog 2. Note: bit 3 of 10 bit value

1

Read frequency of watchdog 2.

2

Read frequency of watchdog 2.

3

Read frequency of watchdog 2.

4

Read frequency of watchdog 2.

5

Read frequency of watchdog 2.

6

Read frequency of watchdog 2.

7

Read frequency of watchdog 2. MSB (bit 9) of 10 bit value, 0-9

Reg 16 IIC \rightarrow reg

bit

0

Select 5 bit audio volume control. LSB Note: - on volume control all L's = Mute

Select 5 bit audio volume control.

1

Select 5 bit audio volume control.

2

3

Select 5 bit audio volume control.

4

Select 5 bit audio volume control. MSB

5

Select alarm, active/reset (L = reset)

6

Select 4.000MHz or 8.000MHz clock speed (L = 8MHz)

Select ANRS defeat (L = no ANRS, H = ANRS)

Reg 17 IIC → reg

bit

Select LNB voltage. 8 bit value. LSB = bit 0

0

L

1

L

Select LNB voltage. 8 bit value. LSB = bit 0

Select LNB voltage. 8 bit value. LSB = bit 0

2

3

L

Select LNB voltage. 8 bit value. LSB = bit 0

Select LNB voltage. 8 bit value. LSB = bit 0

L

5

1

Select LNB voltage. 8 bit value. LSB = bit 0

6

Select LNB voltage. 8 bit value. LSB = bit 0

L

Select LNB voltage. 8 bit value. LSB = bit 0

Reg 18 IIC → reg (read/write)

bit

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

0

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

1

L

2

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

3

L

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

4

L

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

5

Select/Status Time Minutes (0-59) 6 bit value. LSB = bit 0

6

Status of alarm (is it triggered?) H = Triggered

Not used

```

#### **Reg 19 IIC** → **reg** (read/write)

bit

- 0 L Select/Status Time Hours (0-23) 5 bit value. LSB = bit 0

- 1 L Select/Status Time Hours (0-23) 5 bit value. LSB = bit 0

- 2 L Select/Status Time Hours (0-23) 5 bit value. LSB = bit 0

- 3 L Select/Status Time Hours (0-23) 5 bit value. LSB = bit 0

- 4 L Select/Status Time Hours (0-23) 5 bit value. LSB = bit 0

- 5 L Not used

- 6 ? Not used

- 7 ? Not used

# Reg 20 IIC ↔ reg (read/write)

bit

- 0 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 1 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 2 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 3 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 4 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 5 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 6 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

- 7 L Select/Status Time Days (0-255) 8 bit value. LSB = bit 0

### **Reg 21 IIC** ↔ **reg** (read/write)

bit

- 0 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 1 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 2 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 3 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 4 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 5 L Select/Status Alarm Minutes (0-59) 6 bit value. LSB = bit 0

- 6 L Not used

- 7 ? Not used

### Reg 22 IIC ↔ reg (read/write)

bit

- 0 L Select/Status Alarm Hours (0-23) 5 bit value. LSB = bit 0

- 1 L Select/Status Alarm Hours (0-23) 5 bit value. LSB = bit 0

- 2 L Select/Status Alarm Hours (0-23) 5 bit value. LSB = bit 0

- 3 L Select/Status Alarm Hours (0-23) 5 bit value. LSB = bit 0

- 4 L Select/Status Alarm Hours (0-23) 5 bit value. LSB = bit 0

- 5 L Not used

- 6 ? Not used

- 7 ? Not used

#### Reg 23 IIC ↔ reg (read/write)

bit

- 0 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 1 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 2 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 3 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

4 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 4 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

5 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 6 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

- 7 L Select/Status Alarm Days (0-255) 8 bit value. LSB = bit 0

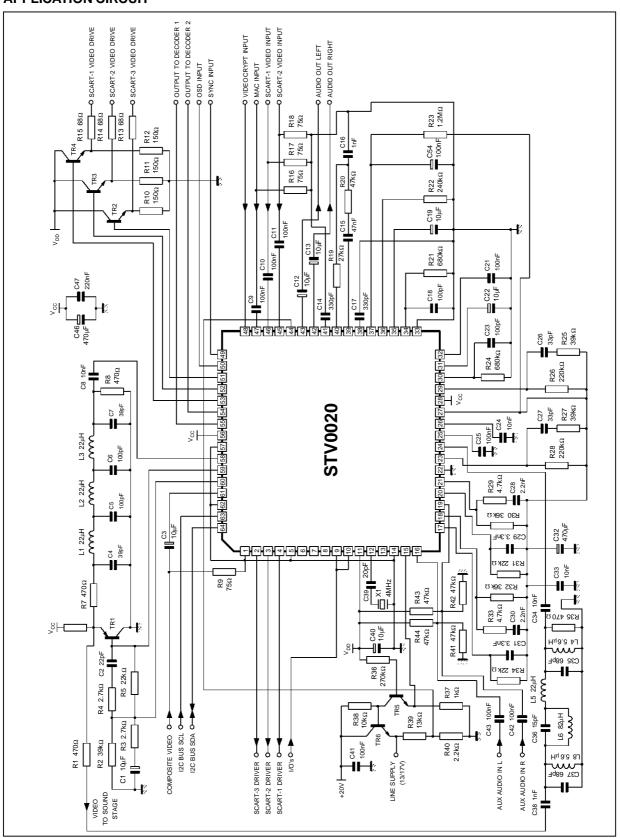

# **APPLICATION CIRCUIT**

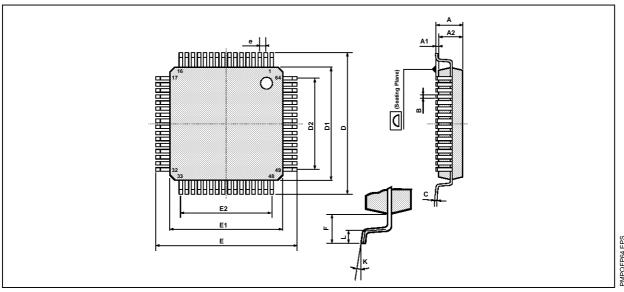

# **PACKAGE MECHANICAL DATA**

64 PINS - PLASTIC QUAD FLAT PACK

| Dimensions |                      | Millimeters |       |       | Inches |       |

|------------|----------------------|-------------|-------|-------|--------|-------|

| Dimensions | Min.                 | Тур.        | Max.  | Min.  | Тур.   | Max.  |

| А          |                      |             | 3.40  |       |        | 0.134 |

| A1         | 0.25                 |             |       | 0.01  |        |       |

| A2         | 2.55                 | 2.80        | 3.05  | 0.10  | 0.11   | 0.12  |

| В          | 0.30                 |             | 0.45  | 0.012 |        | 0.018 |

| С          | 0.13                 |             | 0.23  | 0.005 |        | 0.009 |

| D          | 16.95                | 17.20       | 17.45 | 0.667 | 0.677  | 0.687 |

| D1         | 13.90                | 14.00       | 14.10 | 0.547 | 0.551  | 0.555 |

| D2         |                      | 12.00       |       |       | 0.472  |       |

| е          |                      | 0.80        |       |       | 0.031  |       |

| E          | 16.95                | 17.20       | 17.45 | 0.667 | 0.677  | 0.687 |

| E1         | 13.90                | 14.00       | 14.10 | 0.547 | 0.551  | 0.555 |

| E2         |                      | 12.00       |       |       | 0.472  |       |

| F          |                      | 1.60        |       |       | 0.063  |       |

| K          | 0° (min.), 7° (max.) |             |       |       |        |       |

| L          | 0.65                 | 0.80        | 0.95  | 0.025 | 0.031  | 0.037 |